台积电正在开发一种新的先进芯片封装方法,使用矩形面板基板,以满足对先进多芯片处理器日益增长的需求。这一创新技术仍处于早期阶段,预计需要数年时间才能实现商业化,但如果成功实施,将为这家全球最大的合同芯片制造商带来重大的技术变革。

据报道,台积电的新方法使用了510毫米×515毫米的矩形衬底,而不是传统的300毫米直径晶圆。这些面板的可用面积比传统的300毫米圆晶圆大3.7倍,能够在每个晶圆上生产更多芯片,并减少边缘浪费。然而,这种新方法需要全新的设备,这意味着台积电将无法使用传统的晶圆厂工具。目前,台积电正在与设备和材料供应商合作开发这种新的封装技术,但具体细节尚未透露。

台积电在日经新闻发布的一份声明中写道:“我们密切关注先进封装的进展和发展,包括面板级封装。”

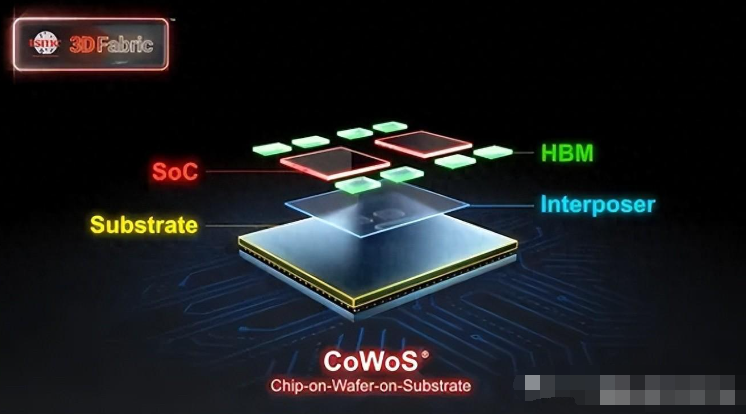

该公司目前的先进芯片封装技术,如CoWoS(

Chip-on-Wafer-on-Substrate),使用300毫米硅片,对于为英伟达、AMD、亚马逊和谷歌等客户生产人工智能处理器至关重要。然而,随着人工智能芯片尺寸和复杂性的增长,现有方法的效率可能会下降,这促使了对新型矩形基板的需求。

向矩形基板的过渡在技术上具有挑战性,需要对生产工具和材料进行重大更改。芯片生产所需的精度高于显示器和PCB制造,使这种转变变得复杂且耗时。

过渡到矩形基板被认为是一个长期计划,可能需要5到10年的时间。为了适应新的基板形状并确保这种先进封装方法的成功,台积电需要对设备进行重大升级,包括更新机械臂和自动化材料处理系统。

台积电雄厚的财力和行业影响力对推动设备制造商适应新环境至关重要,但该计划能否实现仍有待观察。随着台积电在先进封装领域的不断创新,未来芯片生产的效率和性能有望得到显著提升。

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。